Écrire & Comprendre VHDL & AMS

©Jacques Rouillard 2008

ISBN 978-1-4092-3689-4

Imprimé en Espagne ou aux USA

(USA si indiqué en dernière page)

Lulu éditeur

Illustration de couverture: Codex sur le vol des oiseaux Léonard de Vinci - 1485-1490

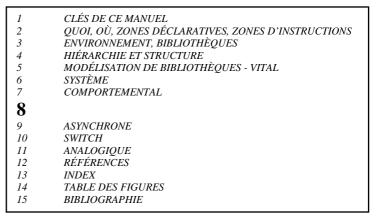

| 1  | CLÉS DE CE MANUEL                                  |

|----|----------------------------------------------------|

| 2  | QUOI, OÙ, ZONES DÉCLARATIVES, ZONES D'INSTRUCTIONS |

| 3  | ENVIRONNEMENT, BIBLIOTHÈQUES                       |

| 4  | HIÉRARCHIE ET STRUCTURE                            |

| 5  | MODÉLISATION DE BIBLIOTHÈQUES - VITAL              |

| 6  | SYSTÈME                                            |

| 7  | COMPORTEMENTAL                                     |

| 8  | SYNCHRONE                                          |

| 9  | ASYNCHRONE                                         |

| 10 | SWITCH                                             |

| 11 | ANALOGIQUE                                         |

| 12 | RÉFÉRENCES                                         |

| 13 | INDEX                                              |

| 14 | TABLE DES FIGURES                                  |

| 15 | DIDLIOCDA DILIE                                    |

# Table des Matières

| 1 | CLÉS           | DE CE MANUEL                                         | 7    |

|---|----------------|------------------------------------------------------|------|

|   | 1.1            | Objectif                                             | 7    |

|   |                | C'ORGANISATION DE CE MANUEL                          |      |

|   | 1.3 L          | ES EXEMPLES DE CE MANUEL                             | 8    |

|   |                | ES PAQUETAGES EN ANNEXE                              |      |

|   |                | ES OUTILS                                            |      |

|   |                | MÉTHODOLOGIES USUELLES                               |      |

|   | 1.6.1          | Conception descendante (Top-Down)                    |      |

|   | 1.6.2          | Conception montante (Bottom-Up)                      |      |

|   | 1.6.3          | Conception montante-descendante (Meet-In-The-Middle) |      |

|   | 1.7 L          | LES VERSIONS DES LANGAGES ET DE L'ENVIRONNEMENT      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1<br>1.7.1 |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.1          |                                                      |      |

|   | 1.7.2          | Les types logiques                                   |      |

|   | 1.7.2          | 7.5                                                  |      |

|   | 1.7.2          |                                                      |      |

|   | 1.7.2          |                                                      |      |

|   | 1.7.2          |                                                      |      |

|   | 1.7.2          |                                                      |      |

|   | 1.7.2<br>1.7.2 | 1 1 0 = =                                            |      |

|   | 1.7.3          | La maintenance du langage et des paquetages          |      |

|   |                |                                                      |      |

| 2 | QUOI,          | , OÙ, ZONES DÉCLARATIVES, ZONES D'INSTRUCTIONS       | . 17 |

|   | 2.1 L          | ES UNITÉS DE COMPILATION                             | . 17 |

|   | 2.1.1          | La déclaration d'entité                              |      |

|   | 2.1.2          | Le corps d'architecture                              |      |

|   | 2.1.3          | La déclaration de paquetage                          |      |

|   | 2.1.4          | Le corps de paquetage                                |      |

|   | 2.1.5          | La déclaration de configuration                      |      |

|   | 2.2 L          | ES INSTRUCTIONS À DÉCLARATIONS LOCALES               |      |

|   | 2.2.1          | <i>Le bloc</i>                                       | 20   |

|   | 2.2.2          | Le processus                                         |      |

|   | 2.2.3          | Le simultané procédural                              | 22   |

|   | 2.2.4          | Le type protégé (moniteur)                           |      |

|   | 2.3 L          | ES SOUS-PROGRAMMES                                   |      |

|   | 2.3.1          | Les arguments                                        | 24   |

|   | 2.3.2          | La procédure                                         | 24   |

|   | 2.3.3          | La fonction                                          | 25   |

| 3 | ENVIRONNEMENT, BIBLIOTHÈQUES                                                       | 27 |

|---|------------------------------------------------------------------------------------|----|

| 4 | HIÉRARCHIE ET STRUCTURE                                                            | 29 |

|   | 4.1 LA GÉNÉRICITÉ                                                                  | 29 |

|   | 4.1.1 L'entité est générique, le composant est pareillement générique              |    |

|   | 4.1.2 L'entité est générique, pas le composant                                     |    |

|   | 4.1.3 L'entité est générique, le composant aussi mais moins                        |    |

|   | 4.2 LES PORTS                                                                      |    |

|   | 4.2.1 L'ordre des ports                                                            |    |

|   | 4.2.2 Forçage                                                                      |    |

|   | 4.2.3 Laisser ouvert (open)                                                        |    |

|   | 4.2.4 Défaut                                                                       |    |

|   | 4.2.5 Changer le type                                                              |    |

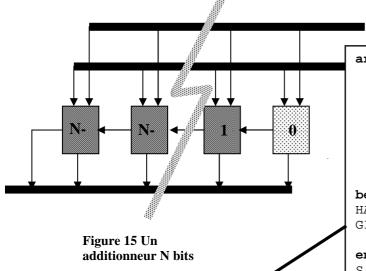

|   | 4.3 GÉNÉRIQUES ET GÉNÉRATION                                                       |    |

| _ |                                                                                    |    |

| 5 | MODÉLISATION DE BIBLIOTHÈQUES - VITAL                                              |    |

|   | 5.1 POURQUOI, COMMENT ?                                                            |    |

|   | 5.2 LE PAQUETAGE VITAL_TIMINGS                                                     |    |

|   | 5.3 LE PAQUETAGE VITAL_PRIMITIVES                                                  |    |

|   | 5.4 LE PAQUETAGE VITAL_MEMORY                                                      |    |

|   | 5.5 UN PETIT EXEMPLE                                                               |    |

|   | 5.5.1 Sans les conventions VITAL                                                   |    |

|   | 5.5.1.1 Fonctionnalité                                                             |    |

|   | 5.5.1.2 Délai simple et unique                                                     |    |

|   | 5.5.1.4 Délais dépendant des varieurs proposees                                    |    |

|   | 5.5.1.5 Délais génériques                                                          |    |

|   | 5.5.2 Avec les conventions VITAL                                                   |    |

|   | 5.5.2.1 Fonctionnalité                                                             |    |

|   | 5.5.2.2 Délais dépendant des fronts                                                |    |

|   | 5.5.2.3 Processus VITAL                                                            |    |

|   | 5.5.2.4 Etc                                                                        |    |

| 6 | SYSTÈME                                                                            | 49 |

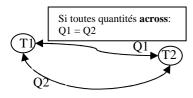

|   | 6.1 ILLUSTRATION                                                                   | 49 |

|   | 6.2 FONCTION DE RÉSOLUTION                                                         | 50 |

|   | 6.3 GÉNÉRATEURS PSEUDO-ALÉATOIRES, VARIABLES PARTAGÉES                             |    |

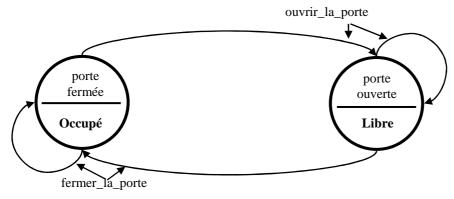

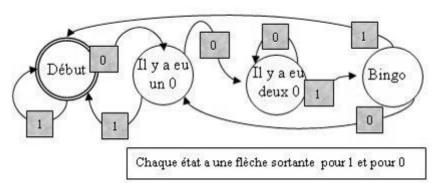

|   | 6.4 Protocole                                                                      | 52 |

|   | 6.5 Tester                                                                         | 54 |

| 7 | COMPORTEMENTAL                                                                     | 57 |

|   | 7.1 COMPORTEMENTAL NON SYNTHÉTISABLE                                               | 57 |

|   | 7.1.1 RAM                                                                          | 57 |

|   | 7.1.2 Grande RAM: optimisation                                                     | 58 |

|   | 7.1.3 Très grande RAM : liste chaînée                                              |    |

|   | 7.1.4 ROM                                                                          |    |

|   | 7.1.4.1 Rom à initialisation par agrégat                                           |    |

|   | 7.1.4.2 Rom à initialisation par fichier                                           |    |

|   | 7.1.4.2.1 Fichier simple binaire                                                   |    |

|   | 7.1.4.2.2 Lecture d un richier au format in Fel.  7.2 Comportemental synthétisable |    |

|   |                                                                                    |    |

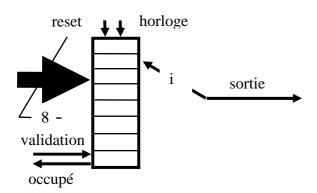

|   | 7.2.1 Conversion parallèle série                                                   |    |

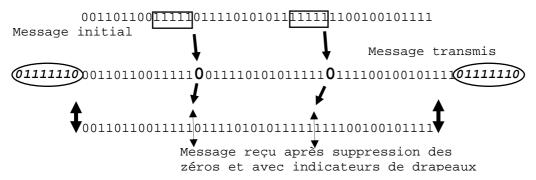

|   | 7.2.2 Drapeau HDLC                                                                 |    |

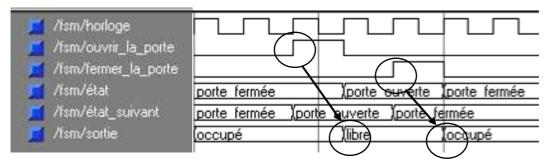

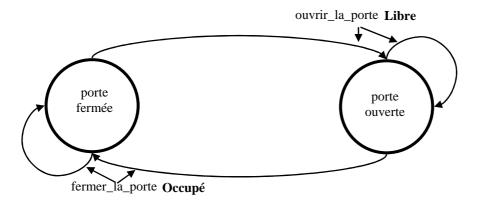

|   | 7.3.1 Machine de Moore                                                             |    |

|   | 7.3.2 Machine de Medvedev                                                          |    |

|   | 7.3.3 Machine de Mealy                                                             |    |

|   | 7.3.4 Machine de Mealy synchronisée                                                |    |

|   | 7.3.5 Codage                                                                       |    |

| 0 |                                                                                    |    |

| 8 | SYNCHRONE                                                                          | 79 |

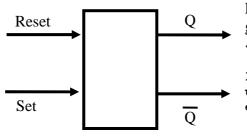

|    | 8.1             | BASCULES                                                                                             |     |

|----|-----------------|------------------------------------------------------------------------------------------------------|-----|

|    | 8.1.1           | Bascule D                                                                                            |     |

|    | 8.1.2           | Latch                                                                                                |     |

|    | 8.1.3           | Bascule RS                                                                                           |     |

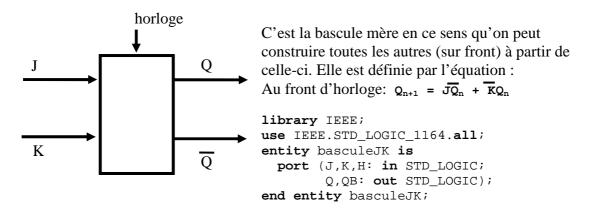

|    | 8.1.4           | Bascule JKCOMBINATOIRE SYNCHRONISÉ                                                                   |     |

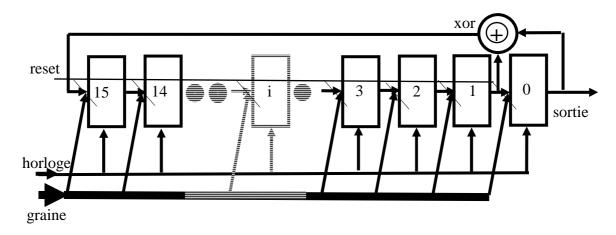

|    | 8.2<br>8.3      | GÉNÉRATEUR DE SÉQUENCES PSEUDO-ALÉATOIRES                                                            |     |

|    | 8.4             | BLOCS GARDÉS                                                                                         |     |

| 9  |                 | NCHRONE                                                                                              |     |

|    | -               |                                                                                                      |     |

|    | 9.1<br>9.1.1    | ASYNCHRONE INONDANT, LE FLOT-DE-DONNÉES (DATA-FLOW)                                                  |     |

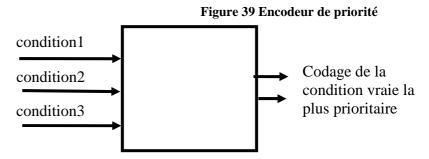

|    | 9.1.1           | L'affectation simple : un fu ou un registre<br>L'affectation conditionnelle: un encodeur de priorité |     |

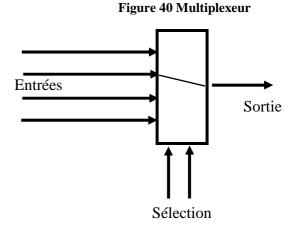

|    | 9.1.3           | L'affectation sélectée: un multiplexeur                                                              |     |

|    | 9.1.4           | L'appel concurrent de procédure : un processus avec des arguments                                    |     |

|    | 9.2             | ASYNCHRONE PROTOCOLAIRE                                                                              |     |

|    | 9.2.1           | Handshake                                                                                            |     |

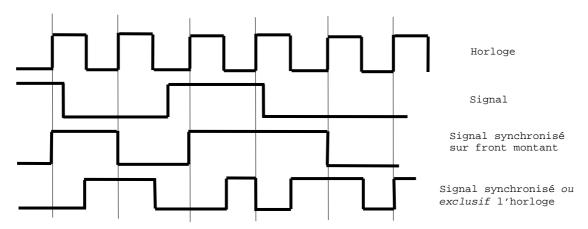

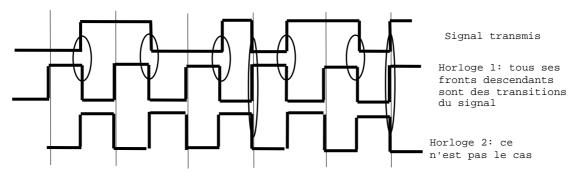

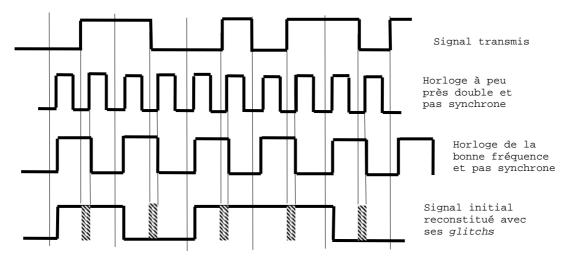

|    | 9.2.2           | Reconstitution d'un signal codé NRZ et de son horloge                                                | 90  |

| 10 | SWI             | TCH                                                                                                  | 95  |

|    | 10.1            | Un modèle de switch                                                                                  | 95  |

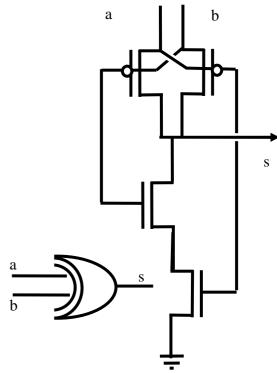

|    | 10.2            | Un « ou exclusif » en switch                                                                         |     |

| 11 | ANA             | LOGIQUE                                                                                              | 00  |

| 11 |                 | -                                                                                                    |     |

|    | 11.1            | OBJETS, INSTRUCTIONS, CONTRAINTES, DOMAINES                                                          |     |

|    | 11.1.           | - · · · · · · · · · · · · · · · · · · ·                                                              |     |

|    | 11.1.2<br>11.1  |                                                                                                      |     |

|    | 11.1            |                                                                                                      |     |

|    |                 | ÉLÉMENTS DE BASE                                                                                     |     |

|    | 11.2.           |                                                                                                      |     |

|    | 11.2.           |                                                                                                      |     |

|    | 11.2            | *                                                                                                    |     |

|    | 11.2.           | <b>y</b>                                                                                             |     |

|    | 11.2            |                                                                                                      |     |

|    | 11.2.0          |                                                                                                      |     |

|    | 11.2.           | T                                                                                                    |     |

|    | 11.2.           |                                                                                                      |     |

|    | 11.2.5<br>11.2. |                                                                                                      |     |

|    | 11.3            | MODÉLISATION MIXTE                                                                                   |     |

|    | 11.3.           |                                                                                                      |     |

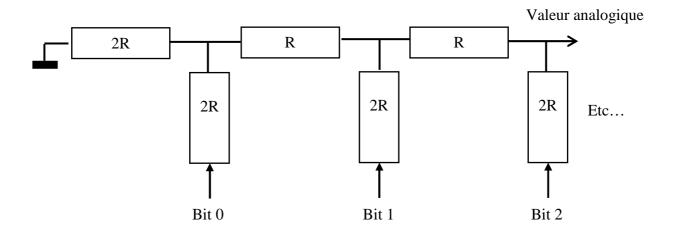

|    | 11              | 3.1.1 Réseau R/2R, structurel                                                                        | 109 |

|    |                 | 3.1.2 Convertisseur Digital-Analogique, comportemental                                               |     |

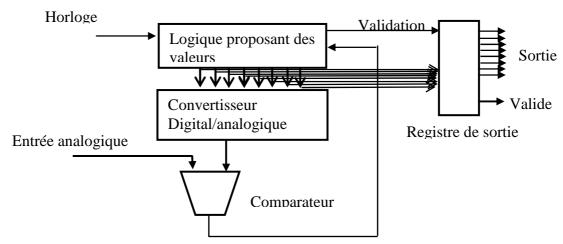

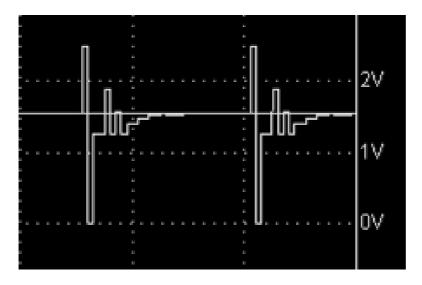

|    | 11.3.2          | 3.1 3                                                                                                |     |

|    |                 | 3.2.1 Comparateur                                                                                    |     |

|    |                 | 3.2.3 Assemblage du convertisseur : modèle structurel mixe analogique/digital                        |     |

| 12 | RÉF             | ÉRENCES                                                                                              |     |

|    | 12.1            | STANDARD ET UTILES                                                                                   | 117 |

|    | 12.1.           |                                                                                                      |     |

|    | 12.1.1          |                                                                                                      |     |

|    | 12.1            |                                                                                                      |     |

|    | 12.2            | IEEE                                                                                                 |     |

|    | 12.2.           | IEEE.STD_LOGIC_1164                                                                                  | 121 |

|    | 12.2.2          |                                                                                                      |     |

|    | 12.2            | <del>-</del>                                                                                         |     |

|    | 12.3            | IEEE-VITAL                                                                                           |     |

|    | 12.3.           |                                                                                                      |     |

|    | 12.3.2          | VITAL_TIMING                                                                                         | 130 |

|                                           | 12.3.3 | VITAL_Primitives                     |     |

|-------------------------------------------|--------|--------------------------------------|-----|

|                                           | 12.3.4 | VITAL MEMORY                         |     |

| 1                                         | 2.4 AN | IALOGIQUE                            | 153 |

|                                           |        | [AMS]IEEE.FUNDAMENTAL_CONSTANTS      |     |

|                                           | 12.4.2 | [AMS] DISCIPLINES.ELECTRICAL_SYSTEMS |     |

| 13                                        | INDEX. |                                      | 157 |

| 14 TABLES DES FIGURES<br>15 BIBLIOGRAPHIE |        |                                      |     |

|                                           |        |                                      |     |

### 1 Clés de ce manuel

## 1.1 Objectif

Ce petit manuel ambitionne de présenter les différentes techniques de modélisation en VHDL, avec des exemples paradigmatiques, en présentant les concepts et techniques liés à VHDL mais

| 1  |                                                    |

|----|----------------------------------------------------|

| 1  |                                                    |

| 2  | QUOI, OÙ, ZONES DÉCLARATIVES, ZONES D'INSTRUCTIONS |

| 3  | ENVIRONNEMENT, BIBLIOTHÈQUES                       |

| 4  | HIÉRARCHIE ET STRUCTURE                            |

| 5  | MODÉLISATION DE BIBLIOTHÈQUES - VITAL              |

| 6  | SYSTÈME                                            |

| 7  | COMPORTEMENTAL                                     |

| 8  | SYNCHRONE                                          |

| 9  | ASYNCHRONE                                         |

| 10 | SWITCH                                             |

| 11 | ANALOGIQUE                                         |

| 12 | RÉFÉRENCES                                         |

| 13 | INDEX                                              |

| 14 | TABLE DES FIGURES                                  |

| 15 | BIBLIOGRAPHIE                                      |

en faisant délibérément l'impasse sur la présentation en détail du langage : le lecteur aura donc besoin d'une connaissance préalable ou d'un autre manuel, par exemple le compagnon de celui-ci « Lire & Comprendre VHDL & AMS qui au contraire parle du langage et non des modèles, et qui est organisé par traits du langage et non par style d'application. Un aide mémoire de 12 pages est à la fin de ce manuel, que l'on pourra découper et agrafer. Il est aussi disponible en *pdf*. (Voir bibliographie [ROU1] et [ROU2], chapitre15 page 161)

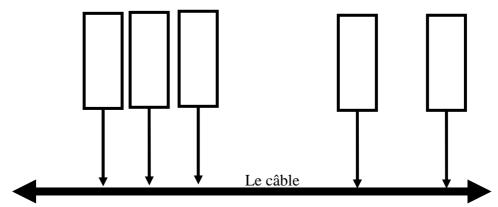

## 1.2 L'organisation de ce manuel

Après une présentation des questions qui transcendent tous les styles (<u>organisation générale</u> <u>du langage</u> **chapitre 2**, <u>bibliothèques</u> **chapitre 3**, <u>hiérarchie</u> **chapitre 4**), les chapitres étudient sur des exemples ad-hoc les niveaux de modélisation qu'on peut attaquer en VHDL : depuis le niveau système, avec l'exemple d'un réseau comportant une centaine de transmetteurs, jusqu'au niveau analogique où l'on s'intéresse au composant lui-même.

- Les niveaux décrits sont :

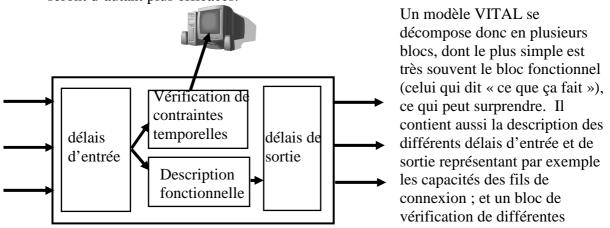

- <u>La modélisation d'éléments de bibliothèque</u>, utilisant le standard VITAL. C'est une modélisation qui est techniquement surtout structurelle, mais qui utilise des conventions très serrées permettant de rétro-annoter les modèles après synthèse, c'est-à-dire d'y insérer des délais de transmission très proches de la réalité, sans avoir à ouvrir les modèles qui se servent de ces briques. **Chapitre 5.**

- <u>Système</u>: niveau où l'on s'intéresse à des abstractions, le temps n'est intéressant qu'en termes de causalité. On simule des systèmes qui représenteront à la fin une très grande quantité de matériel et de logiciel, on fait des statistiques et on envoie des vecteurs de test basés sur des séquences aléatoires. La simulation n'est pas déterministe. **Chapitre 6.**

- Comportemental: on valide des algorithmes, dont on peut ne pas savoir encore s'ils seront implémentés en logiciel ou matériel. On peut aussi écrire des briques qu'on ne réalisera jamais —elles existent déjà ou sont l'objet d'un contrat-, simplement pour faire fonctionner le reste du modèle. Chapitre 7.

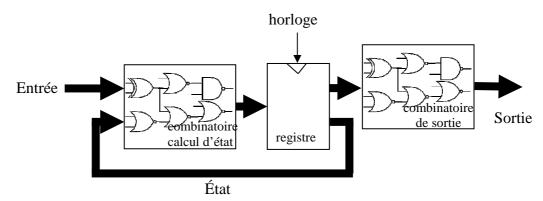

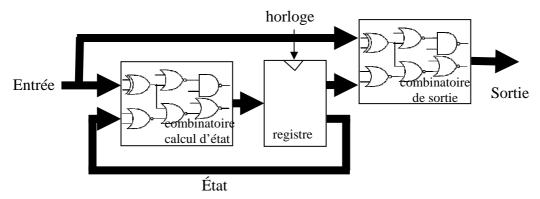

- <u>Synchrone</u>: le temps est mesuré en termes de coups d'horloge. Le circuit est un assemblage de blocs ayant la même horloge; C'est un niveau extrêmement efficace en termes de simulation. **Chapitre 8.**

- Asynchrone: le circuit est décrit, *in fine*, en termes d'équations logiques et le plus généralement les objets manipulés sont de type binaire ou entier se résolvant en codage binaire. On y traite aussi des questions de protocole qui sont en général asynchrones et sans horloge. **Chapitre 9.**

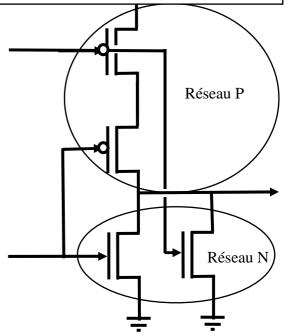

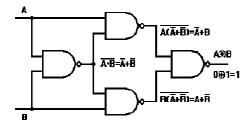

- <u>Switch</u>: c'est un niveau un peu bâtard et anecdotique, qui permet de faire de la logique tout en s'intéressant aux questions de force électrique. Le lecteur intéressé par le cycle de simulation pourra y trouver d'intéressants sujets de réflexion. **Chapitre 10.**

- Analogique: le temps est continu et tout se résout en équations différentielles. VHDL-AMS est une extension de VHDL, et les modèles écrits en AMS sont mixtes. Chapitre 11.

### 1.3 Les exemples de ce manuel

Ils sont là seulement pour exemplifier des constructions et des méthodes, voire des difficultés du langage. Ils sont choisis délibérément très courts, sont en général beaucoup trop simples pour être directement utilisables dans un contexte réel ; et ils ne constituent en aucun cas des projets complets, par contre ils sont fonctionnels et compilables.

Ce manuel n'est donc pas un recueil de modèles, chose qu'on trouvera par ailleurs facilement et en particulier sur Internet. Par ailleurs les exemples donnés sont corrects à la connaissance de l'auteur, mais aucune garantie ni engagement ne sont donnés à ce sujet.

Une mine d'exemples et de modères « réels » seront particulièrement trouvés sur le site : <a href="http://tams-www.informatik.uni-hamburg.de/vhdl/">http://tams-www.informatik.uni-hamburg.de/vhdl/</a>, voir [HAM] en bibliographie chapitre 15 page 161.

## 1.4 Les paquetages en annexe

Les paquetages VHDL donnés en annexe chapitre 12 à partir de la page 115 ne sont pas *tous* les paquetages standardisés, ni *tous* les paquetages libres qui sont dans la nature, mais ceux dont il est raisonnable de faire usage selon l'avis subjectif de l'auteur. Les questions de copyright étant complexes, les versions données ici sont, à la connaissance de l'auteur, ou bien des versions publiques, ou bien les dernières versions de travail publiques utilisées par les comités en principe identiques aux versions finales, aux entêtes près. Dans le cas des paquetages VITAL, les commentaires en ont été retirés car ils triplaient le volume de texte. Le lecteur intéressé par lesdits paquetages in extenso, ou par un paquetage public rare ou exotique le trouvera probablement sur Internet. Certains sont dans le livre compagnon « Lire & Comprendre VHDL & AMS » ; voir la bibliographie [ROU1] chapitre 15 page 161.

#### 1.5 Les outils

Les outils utilisés pour vérifier les exemples de ce manuel sont, pour la partie digitale, les outils disponibles à cette date dans leur version « éducation » de *Mentor Graphics* (*ModelSim*), et pour les modèles mixtes et analogiques, par ordre alphabétique, ceux de *Ansoft* (*Simplorer*), *Dolphin* (*Smash*), et *Mentor-Graphics* (*SimpliVision*).

Quelques différences d'interprétation ou de couverture du langage peuvent nécessiter des adaptations s'ils sont utilisés sur d'autres plateformes que celles où ils ont été testés. À titre indicatif et sans prétendre à l'exhaustivité, on pourra avoir des différences

- sur les caractères accentués : ils sont autorisés mais pas depuis le début de VHDL, certains systèmes ont gardé l'interdiction.

- sur la disponibilité des paquetages non-standard. Ceux mentionnés ici sont tous libres d'accès sur Internet, mais ne sont pas tous des standards IEEE. La solution est simple s'il vient à manquer sur votre plateforme : il suffit de récupérer le paquetage et de le compiler dans la bonne bibliothèque.

- sur le nom des bibliothèques pour l'analogique : DISCIPLINES ou IEEE. Il suffit de modifier la bibliothèque appelée et la clause « use » qui va probablement avec dans le modèle.

- sur les traits coûteux du langage dans certains simulateurs analogiques (types composites de natures, **generate**, **procedural**, **break** dans toute sa fonctionnalité, agrégats en cible d'affectation, ...). L'absence de tableaux de natures et d'instruction **generate** est une vraie limitation qui obligera le concepteur à dérouler « à la main »

les régularités pour chaque configuration possible. C'est surtout handicapant en conception mixte digital/analogique, car les modèles disponibles dans le monde digital qu'on peut avoir envie de réutiliser pour « analogiser » un bloc peuvent faire largement usage des structures et de la génération.

## 1.6 Méthodologies usuelles

## 1.6.1 Conception descendante (*Top-Down*)

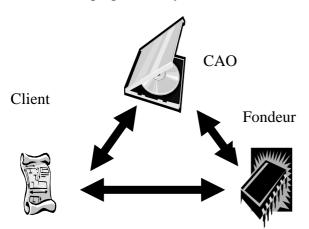

C'est la méthodologie la plus employée dans le cadre commercial le plus courant : un client veut un circuit spécifique, un ASIC (*Application Specific IC*) pour une application, par exemple un DSP spécifique pour un téléphone. Il commande la chose à une maison de conception (*Design-House*) qui est en général une structure moyenne, ou un petit département d'une grosse entreprise, travaillant sur CAO.

La conception se fait alors des spécifications vers le circuit, la validation étant sous le contrôle du client. Les styles employés vont du niveau système au niveau flot-de-données. Dans ce cadre il faut un accord tripartite entre le client, la maison de conception et le fondeur : le *signoff*. Ce contrat est signé entre un vendeur de CAO qui garantit la qualité de ses outils, le fondeur qui garantit que la puce qui sortira sera conforme aux simulations de l'outil de CAO et le client qui paie. S'il y a un souci, c'est le vendeur de CAO et le fondeur qui vont

s'expliquer pour que la sortie de l'usine soit conforme aux prévisions de la CAO. Le contrat fait en sorte que « si ça ne marche pas », ce ne soit pas le client final qui paie la rectification. (Il n'en aurait pas les moyens le plus souvent, vu les coûts de production et la taille des maisons de conception).

Les métiers impliqués sont pour l'essentiel des métiers d'ingénieur de conception « logique », qui connaît le client, a une bonne idée de l'application et ignore la technologie.

Figure 1 Le Sign-Off

### 1.6.2 Conception montante (Bottom-Up)

C'est le cas de figure où un fournisseur cherche à faire un produit « d'étagère »; le meilleur processeur possible pour tel créneau, un circuit spécialisé générique (ex contrôleur d'écran, de disque, décodeur Mpeg...), etc. Le développement se fait en interne avec des spécifications souples que l'on peut remettre en question plus facilement que si l'on avait un contrat à amender. C'est le marché qui valide ensuite.

Aujourd'hui de tels produits sont proposés sous la forme d'IPs (*Intellectual Property*) sous forme entièrement synthétisable multi-cible, ce sont donc des textes VHDL par exemple. Les professionnels sont des ingénieurs de conception « logique » ou « analogique », qui ignorent le client final et ont une idée des applications finales. La technologie peut ou peut ne pas être un paramètre important de la question.

# 1.6.3 Conception montante-descendante (Meet-In-The-Middle)

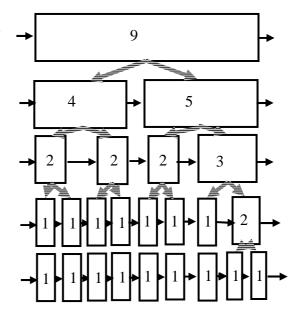

Un fondeur doit développer pour chaque technologie une bibliothèque d'éléments de moyen ou bas-niveau, ou extrêmement génériques, sur laquelle les outils de CAO et en particulier les outils de synthèse vont replier les circuits conçus par les maisons de conception (*Design*-

*Houses*). Ces éléments, demandés par les outils de synthèse, sont conçus comme des briques mais sont eux-mêmes des assemblages de briques, d'où le qualificatif.

Les spécifications sont reconfigurables, « au mieux » de ce qu'on sait faire. Le fondeur maîtrise la technologie et peut donc violer en connaissance de cause les règles qu'il impose à ses clients (paradigme: la cellule de Ram). Il utilisera massivement les paquetages VITAL (chapitre 5, page 37).

La validation est interne ou soumise à un *sign-off* (voir ci-dessus) avec proposition du produit sur « catalogue».

Les ingénieurs impliqués sont des ingénieurs de conception plutôt « analogique » qui ignorent le client final et peuvent ignorer les applications finales ; ils maîtrisent bien la technologie.

# 1.7 Les versions des langages et de l'environnement

### 1.7.1 Les versions des langages

VHDL existe en plusieurs versions dans la nature : les règlements IEEE obligent à revisiter les standards tous les 5 ans –souvent un retard est observé mais il doit être dûment autorisé par les IEEE. Le numéro du standard est 1076. On a ainsi :

#### 1.7.1.1 VHDL 7.2

C'est l'ancêtre du standard dans sa version 7.2 (il y a donc eu des versions antérieures) qui était classifié « défense » et qui ne doit plus guère exister. Ce langage était lui-même un sousproduit d'un énorme projet militaire « VHSIC » (Very High Speed Integrated Circuits) vers 1983, d'où le nom de VHDL (VHSIC Hardware Description Langage), le « langage de description de matériel du projet VHSIC », c'est donc un acronyme d'acronymes. Le même DoD avait créé de toutes pièces le langage Ada, et à cette époque Ada influençait tous les développements logiciels militaires américains. La dernière implémentation de VHDL 7.2 (connue de l'auteur) était écrite en Ada et produisait de l'Ada qu'il fallait encore recompiler, ce qui n'était pas rapide –euphémisme-. Elle a servi de base au prototype du premier compilateur VHDL 1076.

#### 1.7.1.2 VHDL 1076-1987

C'est le standard IEEE initial, standard créé de toutes pièces sur la base du précédent par décision du DoD (ministère de la défense américain) qui a mis VHDL7.2 dans le domaine public en 1985, a payé pendant plusieurs années des sociétés —principalement CLSI—pour envoyer des ingénieurs aux comités IEEE, transformer VHDL 7.2 en standard, faire développer un prototype et gérer le vote initial.

#### 1.7.1.3 VHDL 1076-1991 (Interprétations)

Le standard sous la forme "papier" contenait quelques bogues bloquantes pour le développement des premiers compilateurs, par exemple la visibilité des arguments génériques dans la déclaration des ports qui suivait immédiatement n'était pas assurée. Ainsi qu'il est expliqué au §1.7.3 ci-dessous, un comité technique (ISAC) chargé de la maintenance du langage émettait des interprétations validées par le VASG. Celles-ci sont rassemblées dans ce document qui n'est pas une nouvelle version du standard, mais la « vue du comité », (Sense of the VASG) sur le traitement de ces anomalies.

#### 1.7.1.4 VHDL 1076-1993

La première révision qui propose des modifications majeures. Cette révision a rassemblé toutes les corrections importantes nécessaires ou désirées par la première génération

d'utilisateurs et de développeurs, en particulier celles du document précédent. On y trouve aussi les variables partagées, une simplification de la gestion de fichiers, les opérateurs de rotation et de décalage, les identificateurs étendus, et bien d'autres nouvelles fonctionnalités ou réparations. C'est cette version qui fait office de référence pour la plupart des outils existants.

#### 1.7.1.5 VHDL-AMS 1076.1-1999

Le standard strict sur-ensemble de VHDL 1993, permettant de traiter l'analogique. Son utilisation est traitée dans le chapitre 11 page 97. En principe, la seule source d'incompatibilité entre VHDL 1076-1993 et VHDL 1076.1-1999 (dans le sens 1076 vers 1076.1) est l'existence de mots réservés supplémentaires. En pratique, les sociétés fournissant des simulateurs analogiques « adaptés » à VHDL.1 font parfois l'impasse sur les traits les plus coûteux du langage.

#### 1.7.1.6 VHDL 1076-2000

Version pratiquement dédiée aux variables partagées, dont l'introduction en 1993 avait fait l'objet d'une guerre de tranchées entre membres des comités et d'un emballement de passions dont seuls sont capables les concepteurs de langages<sup>1</sup>. On y trouve l'introduction des types protégés, les variables partagées doivent maintenant être de ces types. Ceci permettant une paix des braves et l'accès « propre » à de la mémoire partagée dans le cas de simulateurs multi-processeurs.

#### 1.7.1.7 VHDL 1076-2002

Changement d'utilisations des ports de mode buffer et quelques révisions mineures.

#### 1.7.1.8 VHDL-AMS 1076.1-2007

Révisions mineures de VHDL 1076.1-1999, pour ce qui est de la partie analogique du standard, prenant par contre en compte toutes les modifications faites à VHDL 1076 en 2000 et 2002.

#### 1.7.1.9 VHDL 1076-2008

VHDL 2008 est le projet qui vient d'être voté à cette date, qui est une révision majeure et dont aucun outil n'existe encore, voir [ASH2] en bibliographie chapitre 15 page 161. Son existence va automatiquement entraîner une nouvelle version du standard analogique VHDL-AMS 1076.1 dans un avenir proche, puisque ce dernier est défini comme étant un surensemble de VHDL 1076.

Il contient entre autres suppléments

- un langage d'assertions<sup>2</sup> (PSL),

- une méthode pour crypter des portions de la description, de façon à ce que les outils puissent la traiter mais sans que le client ne puisse la lire,

- une interface procédurale permettant d'écrire des outils qui s'interfacent avec les simulateurs,

<sup>1</sup> En effet, la variable partagée casse une propriété essentielle de VHDL: elle permet de rendre l'exécution dépendante de l'ordre d'exécution des processus. À son actif, elle est indispensable pour modéliser des phénomènes stochastiques.

<sup>&</sup>lt;sup>2</sup> Un langage d'assertion permet d'exprimer des vérifications de propriétés qui doivent être toujours vraies. Par exemple « jamais tel signal et tel autre signal ne sont ensemble à un sur le front montant de l'horloge ». L'instruction « assert » de VHDL, les processus retardés (postponed) et la possibilité d'écrire des processus passifs (n'affectant aucun signal) dans la déclaration d'entité sont déjà, en VHDL 1993, un embryon de langage d'assertions.

- la possibilité de rendre un processus sensible sur tous les signaux qui sont dedans, pour être sûr de ne pas en oublier et aller gaiement à la synthèse: process(all);

- la possibilité de mettre des expressions dans les port map, (s'il s'agit d'expressions de signaux);

- force et release de signaux, permettant de coller un signal à une valeur indépendamment du reste de la description;

- la possibilité d'utiliser des types comme arguments génériques (ceci est bien commode, par exemple décrire un multiplexeur ne devrait pas exiger qu'on connaisse le type des données qui circulent). Et la possibilité de faire des paquetages génériques (pour, par exemple, développer des paquetages arithmétiques indépendants du nombre de bits de l'instance). Pour illustration, cette limitation actuelle doit être contournée dans l'exemple décrit en §7.1.4.2.2 page 62;

- la possibilité d'avoir des tableaux et des enregistrements de types non-contraints. Les versions antérieures ne permettent pas de déclarer un tableau "array (integer range 1 to 5) of STRING": il est possible avant 2008 de déclarer un tableau non contraint, mais pas ses éléments qui doivent être contraints;

- diverses simplifications comme la gestion du *don't care* dans les instructions **case**? (une variante du **case**). Ainsi une clause when "01---" couvre toutes les combinaisons de 5 bits commençant par 01;

- l'utilisation de types comme STD\_LOGIC en place de booléen (if S1 and S2 à la place de if S1='1' and S2='1');

- les expressions conditionnelles (affectation conditionnelle comme S <= A when condition else B; autorisée en contexte séquentiel);

- les opérateurs de réduction (S <= and T; où T est un tableau de bits, devient équivalent à S <= T(0) and T(1) and etc.);

- de nouveaux opérateurs, préfixés par un "?" permettant des comparaisons "logiques", par exemple dans le type STD\_LOGIC la comparaison entre *un* fort et *un* faible "'1' ?= 'H'" rendra '1';

- différents paquetages mathématiques implémentant l'arithmétique sur des représentations normalisées de flottant à virgule fixe ou à précision relative;

- des primitives permettant d'avoir une vue textuelle de tous les types (fonctionnalité de l'attribut IMAGE existant);

- des paquetages mathématiques et la façon de les utiliser;

- ...et bien d'autres choses.

- La liste des mots-réservés est de plus en plus importante, et le concepteur utilisant une version antérieure devrait, dans la limite du raisonnable, éviter d'employer des identificateurs qui entreront fatalement en collision avec des mots-clés des futures versions. Cette liste est augmentée de: assume assume\_guarantee context cover fairness force parameter property release restrict restrict\_guarantee sequence strong vmode vprop vunit

#### 1.7.1.10 Portabilité entre versions

Ceci implique que l'on doit souvent se préoccuper de régler la version du langage utilisée. Rassurons nous, à part quelques traits rarement utilisés (types protégés), la question se résume le plus souvent, en attendant les implémentations de VHDL 2008, à choisir entre la version 87 et une autre, essentiellement à cause de la gestion de fichiers qui est incompatible. Parfois un mot-clé apparu dans une version ultérieure pourra entrer en collision avec un nom déclaré dans la version antérieure (**shared** par exemple).

On mentionnera donc ici, à l'occasion, des limitations de la version originale antérieure à VHDL'93. Même si 1993 peut sembler déjà bien loin pour qu'on se préoccupe encore de 1987, il ne faut pas perdre de vue que c'est simplement la date de la standardisation, les outils sont apparus plus tard et, notamment en synthèse où l'on travaille de toutes façons avec des sous-ensemble du langage, courir après les modifications souvent cosmétiques n'est pas la priorité des développeurs d'outils. Bien des outils contiennent encore des traits du langage antérieurs à VHDL'93.

### 1.7.2 Les types logiques

Parallèlement aux travaux sur le langage se tenaient des travaux sur la définition de types logiques. VHDL est le premier et le seul langage de modélisation qui permette, *dans le langage*, de définir une logique (0, 1, X, etc), ses opérateurs (**and**, **or**, etc.) et son comportement en cas de conflit (fonctions de résolution, notion de haute impédance, niveaux forts et faibles). Les autres langages proposent un type logique supposé suffisant pour décrire des circuits électroniques, fournissant grosso-modo les fonctionnalités de STD\_LOGIC\_1164.

Ceci a entraîné trois graves inconvénients :

- Chaque ingénieur ayant son idée sur ce qu'est le meilleur type logique, une profusion de paquetages se sont trouvés sur le marché, provenant d'universitaires ou suggérés par les vendeurs de CAO, chacun défendant mordicus son idée, ce qui tuait partiellement un des bénéfices de VHDL : sa portabilité.

- Les langages concurrents furent vus comme « plus simples » de ce fait.

- Les vendeurs de CAO VHDL ne pouvaient pas optimiser leurs outils pour un type particulier.

Ainsi, pour mémoire, a-t-on vu les paquetages logiques suivants, entre multiples autres.

### 1.7.2.1 Deux états

C'est le paquetage STD.STANDARD, qui propose la logique à deux états '0' et '1', avec le sens de logique positive, et où les conflits sont interdits.

#### 1.7.2.2 Quatre états

'0', '1', 'Z', 'X': les deux états '0' et '1' ont leur sens évident, 'Z' est la haute impédance et permet d'écrire des fonctions de résolution gérant des bus. 'X' représente un conflit entre '0' et '1', ou, selon les implémentations, entre deux valeurs quelconques autres que 'Z'. En effet, on peut décréter raisonnablement qu'il est anormal que deux portes logiques écrivent sur le même fil, y compris si c'est la même valeur.

#### 1.7.2.3 Six états

Les valeurs 0 et 1 du précédent étant distinguées en 0 faible, 0 fort, 1 faible et 1 fort, ceci permettant la modélisation de *pull-ups* et de bus dits « à drain ouvert ».

### 1.7.2.4 Neuf états

L'ancêtre du standard STD\_LOGIC\_1164, alors appelé MVL-9 (*multi-valued-logic*) et qui fut « donné » aux IEEE par le vendeur – *Synopsys*- qui l'avait développé. Voir ci-dessous.

#### 1.7.2.5 Quarante six états

Dans ce système défendu par *Coelho* (Voir [COE] en bibliographie chapitre 15 page 161) et promu par la feue société *Vantage*, les quarante six états n'étaient pas les valeurs mais des possibilités de valeurs : ils étaient l'ensemble des combinaisons contigües de neuf valeurs

possibles : (F) zéro forcé, (R) zéro fort, (W) zéro faible, (Z) zéro haute impédance<sup>3</sup>, (D) déconnection, et de même un haute impédance, un faible, un fort, un forcé. Ainsi l'état WD0, valeur 0 à cheval sur W et D, représentait la possibilité pour le signal d'avoir une valeur zéro faible ou zéro haute impédance. Là-dessus toute la logique pouvait être définie, ainsi que les fonctions de résolution; ce système était particulièrement adapté à la modélisation en niveau switch (voir chapitre 10 page 95 pour une vue de la question utilisant STD\_LOGIC\_1164).

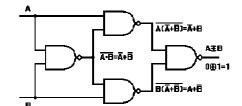

### 1.7.2.6 Le paquetage STD\_LOGIC\_1164

Pour mettre un terme à ce désordre, le paquetage STD\_LOGIC\_1164 a été normalisé. On en trouvera la déclaration dans les références, §12.2.1 page 119. C'est un paquetage à neuf valeurs, distinguant 0, 1 et conflits forts et faibles, un état de haute impédance, un état 'U' disant que l'objet n'a pas été initialisé, et un état '-' utilisé, avant VHDL 2008, uniquement en synthèse pour dire « don't care ». En VHDL 2008, le '-' peut être utilisé dans une instruction case pour couvrir tous les cas de figure correspondants, voir §1.7.1.9 ci-dessus. Depuis l'arrivée de ce standard « libérateur », rarissimes sont les concepteurs qui ne s'en servent pas. La possibilité de définir soi-même sa propre logique et ses propres fonctions résolution est aujourd'hui réservée aux concepteurs systèmes (voir 6.2 page 50 pour une fonction de résolution), aux testeurs d'idées en logique floue et autres originaux... Néanmoins la fonctionnalité existe.

#### 1.7.2.7 Interopérabilité

Certainement d'autres types logiques hantent encore des modèles à maintenir. La possibilité d'écrire ses propres types logiques et les questions d'interopérabilité avait été réglée dans le standard initial par la possibilité d'appeler des fonctions de conversion lors des « **port map** », au vol. Ainsi il est possible d'instancier un composant utilisant 46 états dans un modèle qui n'en a que 9, pour autant qu'on dispose des fonctions de conversions dans les deux sens, en écrivant quelque chose comme:

port map (to\_46\_values(p46) => to\_std\_logic(pstd))

Ici to\_46\_values est une fonction qui prend un élément de type STD\_LOGIC et propose une valeur dans le type à 46 valeurs. to\_std\_logic fait l'inverse. P46 et PSTD sont respectivement des objets de type à 46 ou 9 valeurs.

Ceci est évidemment un pis-aller, puisque la conversion va forcément perdre de l'information. De plus, l'appel de ces fonctions par le simulateur doit être fait au gré des événements et en fonction des modes (in, out, inout), et cela devient rapidement une usine à gaz. Depuis l'arrivée du paquetage STD\_LOGIC\_1164, cette fonctionnalité est rarement utilisée. Hélas, c'est une aventure qui peut arriver au concepteur s'il doit récupérer un ancien modèle. Ce sujet est traité §4.2.5 page 34.

### 1.7.3 La maintenance du langage et des paquetages

VHDL comme bien d'autres standards est un standard vivant, certains comités ont la charge de corriger les défauts ou bogues du manuel de référence, et aussi de rassembler les demandes de modifications pour la révision suivante. Le résultat du travail de ces comités peut prendre plusieurs formes :

• en cas de bogue bloquante, une recommandation est émise et applicable immédiatement. C'est arrivé par exemple quand on s'est rendu compte de certains problèmes de visibilités incorrectement décrits dans le LRM et qui bloquaient directement le développement des compilateurs, voir le résultat au §1.7.1.3 ci-dessus. Ce n'est plus arrivé depuis longtemps.

\_

<sup>&</sup>lt;sup>3</sup> Cela signifie que la valeur est zéro par conservation capacitive de la valeur précédente.

- en cas d'erreur non bloquante, la recommandation est mise en conserve pour inclusion dans la prochaine révision. Par exemple le fait que la fonction ENDLINE du paquetage TEXTIO initial ait été illégale en VHDL (son argument était de classe variable) n'a été découvert qu'après la première standardisation<sup>4</sup>. Cette fonction a été supprimée. On peut donc la retrouver dans d'anciens modèles, les compilateurs de l'époque ayant dû faire une verrue pour cette fonction.

- en cas de trait inesthétique ou mal bâti, une discussion est engagée pour la résolution qui est incluse dans la prochaine révision. La notion de « bit string » a ainsi été étendue à des types non prédéfinis afin de permettre l'utilisation des notations octale et hexadécimale pour les littéraux de std\_logic\_vector. Ce n'était possible que pour bit\_vector en VHDL'87.

- en cas de demande de nouvelle fonctionnalité, tous les cinq ans –à peu près- un appel à propositions est publié, une compilation en est faite, des propositions sont émises et un vote a lieu qui doit enregistrer une super-majorité. Ceux qui votent *non* doivent dire pourquoi, et dire ce qui les ferait voter *oui*; le comité doit tenter de répondre à tous les votes négatifs et tenter de les faire changer d'avis. Ce système a donc assez peu à voir avec un scrutin politique.

Le comité « mère » de tous les autres, le VASG (VHDL Analysis & Standardization Group) et son organe technique ISAC (Issue Screening & Analysis Committee), qui s'occupent de VHDL en tant que langage et dont les travaux ont un effet sur tous les standards dérivés comme VHDL-AMS (l'analogique, voir chapitre 11 page 97) ; et même les standards « en VHDL » comme STD\_LOGIC-1164 (§12.2.1 page 119), WAVES<sup>5</sup> ou VITAL (§12.3 page 125), etc. Ces comités peuvent être contacté par n'importe qui et les sites, à cette date, sont : <a href="http://www.vhdl.org/vasg/">http://www.vhdl.org/vasg/</a> et <a href="http://www.vhdl.org/isac/">http://www.vhdl.org/vasg/</a> et <a href="http://www.vhdl.org/isac/">http://www.vhdl.org/isac/</a>. Les industriels et les clients peuvent anticiper les modifications en consultant les documents de ces comités qui décrivent ce qui sera probablement soumis au vote de la prochaine révision.

Cette activité étant le fait de volontaires (soit à titre personnel, soit mandatés par leur société mais nominalement, il n'y a pas de siège appartenant à une société), il ne faut donc pas s'attendre à une réponse immédiatement efficace. Par contre n'importe qui peut se porter volontaire pour aller dans les réunions et prendre sa part de travail. Pour pouvoir voter sur le standard, il faut être membre IEEE.

Le langage VHDL en tant que tel est vu en détail dans le manuel compagnon de celui-ci « Lire & Comprendre VHDL & AMS » (voir bibliographie [ROU1], chapitre15 page 161) où l'on tente de couvrir tous les traits du langage, car on est souvent amené à lire et tenter de comprendre ce qu'on n'écrirait jamais.

Le passionné ou concepteur d'outils aura besoin du manuel ultime, le LRM (*Language Reference Manual*, (voir la bibliographie [IE1] chapitre 15 page 161), mais insistons sur le fait que ce LRM est d'une absolue inutilité pour le concepteur normal : il contient la description du langage à l'usage des développeurs de compilateurs.

\_

<sup>&</sup>lt;sup>4</sup> Ce qui montre bien que, contrairement à la plupart des langages où c'est l'implémentation du prototype qui tient lieu de première spécification, les premiers compilateurs VHDL sont sortis *après* la publication du manuel de référence, cette erreur ayant été signalée tout à fait normalement par un des premiers compilateurs.

<sup>&</sup>lt;sup>5</sup> WAVES est un standard « en VHDL » qui permet de spécifier des vecteurs de test pour un modèle, les résultats attendus et d'automatiser le test d'une façon qui est compatible avec le testeur qui sera utilisé pour tester le vrai circuit. Il n'est pas couvert par ce manuel. Voir Bibliographie [IE5] chapitre 15 page 163.

# 2 Quoi, où, zones déclaratives, zones d'instructions

D'une façon générale, la plupart des constructions comprennent une partie déclarative et une partie instructions. Il y a un jeu de déclarations qui sont admissibles dans toutes les parties déclaratives,

```

CLÉS DE CE MANUEL

2

ENVIRONNEMENT, BIBLIOTHÈQUES

HIÉRARCHIE ET STRUCTURE

5

MODÉLISATION DE BIBLIOTHÈQUES - VITAL

6

SYSTÈME

COMPORTEMENTAL

SYNCHRONE

ASYNCHRONE

10

SWITCH

ANALOGIQUE

12

RÉFÉRENCES

13

INDEX

TABLE DES FIGURES

14

15

BIBLIOGRAPHIE

```

et d'autres qui dépendent du domaine où l'on se trouve (concurrent, séquentiel).

Les déclarations qui sont universellement acceptées sont :

- Les déclarations qui contrôlent la visibilité : clauses use, alias

- Les déclarations de type, sous-types, constantes, fichiers.

- Les déclarations et spécifications d'attributs, de groupes (usage rare).

- Les spécifications (seulement) de sous-programmes les corps de sous-programmes sont aussi acceptés partout sauf dans les déclarations de paquetage et les spécifications de types protégés.

Nous les appellerons ci-dessous déclarations générales pour éviter d'avoir à répéter ce paquet.

# 2.1 Les unités de compilation

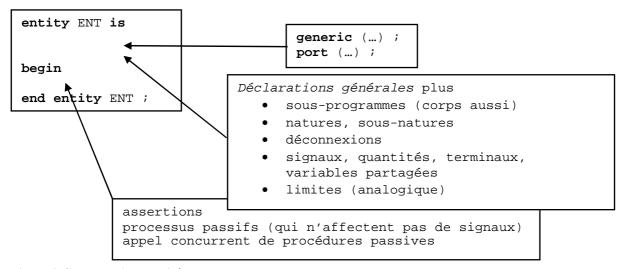

#### 2.1.1 La déclaration d'entité

C'est une des cinq unités (une chose compilable en tant que telle) ; on peut la préfixer par des appels de bibliothèques (clause **library**) et des clauses **use**. La déclaration d'entité peut être vide : tout ce qui suit est optionnel.

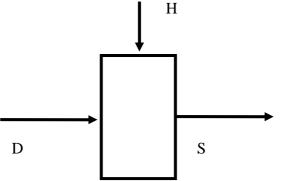

Figure 2 Contenu d'une entité

La déclaration d'entité contient le plus généralement ses spécifications d'interface : les arguments génériques, et les ports. Ce sont les moyens qu'on a de configurer l'entité et de l'appeler depuis l'extérieur.

Mais l'entité peut aussi contenir une quantité de déclarations qui seront vues par toutes ses architectures : des instructions de visibilité (clause use) ou des déclarations de types, soustypes, même des objets comme des signaux, des quantités ou des variables partagées.

Après le **begin** (optionnel donc), la déclaration d'entité peut contenir des instructions, pour autant que ces instructions ne créent pas d'événements et ne participent pas à la simulation : ce sont les assertions (plus utiles dans leur variante retardée - *postponed*) et les processus passifs —qui n'affectent as de signaux- dont le seul effet est de créer des traces à la console ou de remplir des fichiers.

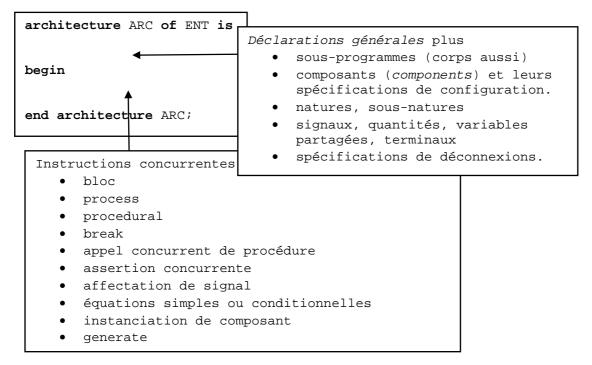

## 2.1.2 Le corps d'architecture

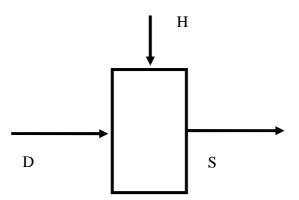

C'est une des cinq unités (une chose compilable en tant que telle) ; on peut la préfixer par des appels de bibliothèques (clause **library**) et des clauses **use**. Le corps d'architecture a lui aussi une partie déclarative et une partie instructions, qui peuvent être vides mais séparées par le mot-clé **begin** qui n'est pas ici optionnel.

La partie déclarative peut contenir, en sus des déclarations générales, celles qui sont spécifiques au domaine concurrent : ce qui a trait au composant (déclaration, configuration), les objets « concurrents » : signaux, quantités, variables partagées et ce qui a trait aux signaux (déconnexion des signaux gardés).

Figure 3 Contenu d'une architecture

La partie instruction ne contient que des instructions concurrentes (c'est-à-dire que leur ordre d'écriture respectif n'a pas de sens pour ce qui est de la description).

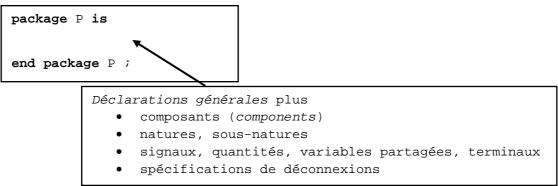

### 2.1.3 La déclaration de paquetage

C'est une des cinq unités (une chose compilable en tant que telle) ; on peut la préfixer par des appels de bibliothèques (clause **library**) et des clauses **use**. C'est une zone purement déclarative, le seul endroit où l'on ait le droit d'écrire une déclaration de sous-programme sans pouvoir en écrire le corps. Comme le paquetage peut être appelé depuis une entité ou une architecture, c'est une zone déclarative concurrente, et on peut y mettre :

Figure 4 Contenu d'une déclaration de paquetage

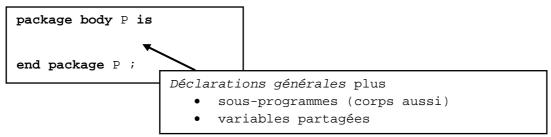

### 2.1.4 Le corps de paquetage

C'est une des cinq unités (une chose compilable en tant que telle). Le corps de paquetage est simplement censé implémenter sa propre déclaration. On y trouve bien entendu toutes les déclarations générales plus les corps de sous-programme (qu'on ne pouvait pas mettre dans la déclaration). Des variables partagées peuvent être déclarées et utilisées par les sous-programmes du paquetage. Mais pas de signaux, de terminaux ou de quantités dont on ne saurait que faire.

Figure 5 Contenu d'un corps de paquetage

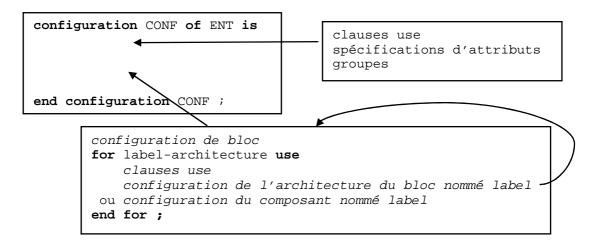

### 2.1.5 La déclaration de configuration

C'est une des cinq unités (une chose compilable en tant que telle); on peut la préfixer par des appels de bibliothèques (clause **library**) et des clauses **use**. C'est une construction qui permet d'associer, de l'extérieur, chaque composant d'une architecture à un couple entité/architecture ou à une autre configuration, et ceci transitivement. À chaque étage, on ouvre la visibilité dans le bloc ou l'architecture ouverte, réglée éventuellement par des clauses use; et soit on donne le nom (label) d'une architecture ou d'un bloc de niveau inférieur, et c'est reparti pour une configuration, soit on donne le nom (label) d'un composant et la transitivité se termine ici.

Figure 6 Contenu d'une déclaration de configuration

#### 2.2 Les instructions à déclarations locales

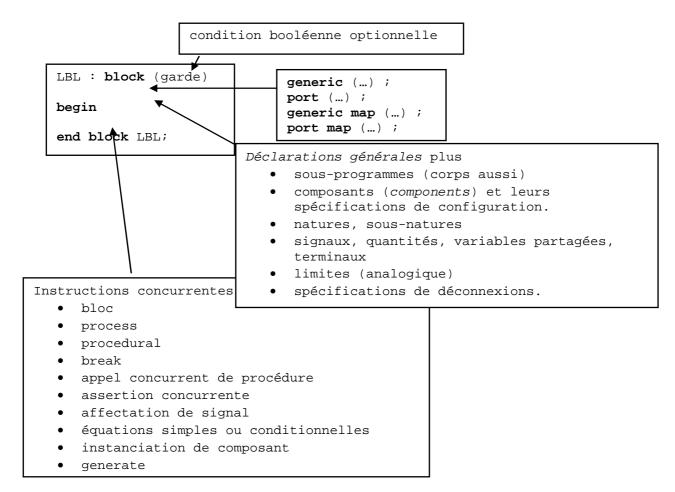

#### 2.2.1 Le bloc

Le bloc est une des instructions qui peut apparaître dans l'architecture ; il est un usage très restreint en VHDL, et il n'est mentionné ici que pour la complétude : il ne sert qu'à créer une zone déclarative quand on en a besoin dans une instruction **generate**, ou à utiliser « la garde », trait de VHDL qui tombe en désuétude (voir §8.4 page 83). Le bloc à lui tout seul récapitule les fonctionnalités de l'entité et de l'architecture, il fait une découpe arbitraire dans le code en nommant les fils de l'interface.

Il a des arguments génériques et des ports, que l'on configure sur le champ avec des **generic map** et **port map**. L'intérêt de cette fonctionnalité surprenante est que la sémantique de l'instanciation est entièrement décrite en blocs équivalents<sup>6</sup>, et que cela permet de décrire de multiples instances de la même entité/architecture comme des duplications de code ; le passage aux signaux réels étant fait au fil de l'eau par les **port map**.

On voit sur la figure que le bloc peut contenir d'autres blocs. L'architecture elle-même n'est finalement qu'un bloc de premier niveau, les déclarations et instructions qu'on peut y mettre sont les mêmes.

\_

<sup>&</sup>lt;sup>6</sup> Ce qui permet de simplifier le manuel de référence, qui explicite seulement la sémantique du bloc; toutes les fonctions d'instanciation se ramenant à des constructions lexicalement équivalentes.

Figure 7 Contenu d'un bloc

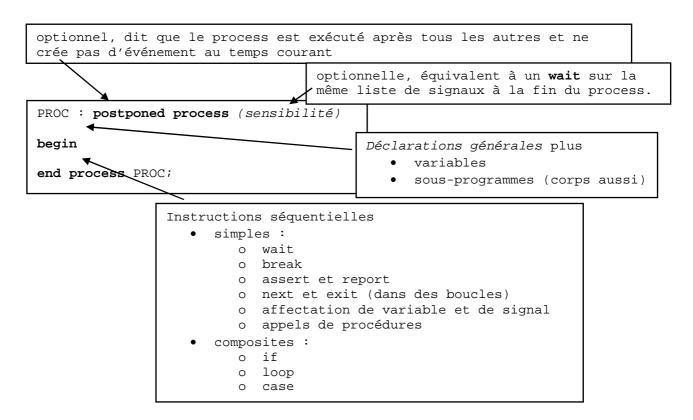

### 2.2.2 Le processus

Le processus (*process*) est une des instructions concurrentes. À ce titre, sa position dans le code vis-à-vis des autres instructions concurrentes n'a pas d'importance.

Le processus contient des instructions séquentielles. Ces instructions là, à l'intérieur des zones séquentielles, sont exécutées dans l'ordre qui a donc de l'importance. Le processus peut être retardé (*postponed*) ce qui permet d'être assuré qu'il sera exécuté une fois et une seule par temps où il est réveillé, quand tous les signaux sont stables. Évidemment la condition de validité est qu'il n'affecte pas de signal avec un délai nul.

La liste de sensibilité est une liste de signaux dont le changement de valeur va réveiller le processus. Sa présence empêche de mettre des **wait** explicites dans le processus. Cette forme est préférée des outils de synthèse, bien que (ou car) plus contraignante.

Figure 8 Contenu d'un processus

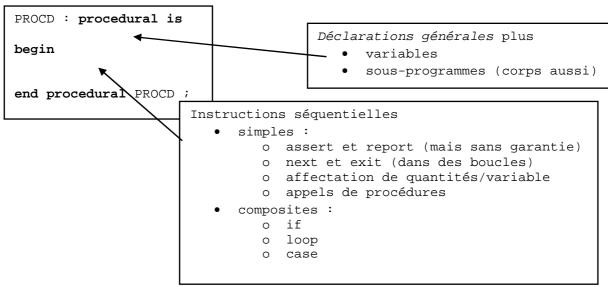

### 2.2.3 Le simultané procédural

Le *procedural* est une instruction simultanée et, comme le processus, sa position parmi les autres instructions concurrentes et simultanées n'a pas d'importance. Le *procedural* contient des instructions séquentielles. Ces instructions là, comme dans le cas du processus, sont exécutées dans l'ordre qui a de l'importance. Le *procedural* est appelé à la discrétion du noyau analogique, autant de fois qu'il veut et quand il veut, avec pour but de faire en sorte que les quantités qui y sont affectées ne changent pas (trop) entre deux exécutions successives du même instant de simulation.

Figure 9 Contenu d'un procedural

Les quantités y sont vues comme des variables, et affectées comme telles avec le signe « := ». Les instructions y sont tout le jeu des instructions séquentielles sauf celles qui interfèrent avec le temps et les événements sur signaux : wait, break, affectation de signal.

Les instructions **assert** et **report** y sont légales mais la norme ne dit pas si elles sont exécutées à chaque exécution du noyau, ou « mises en conserve » d'une façon ou d'une autre pour un effet unique.

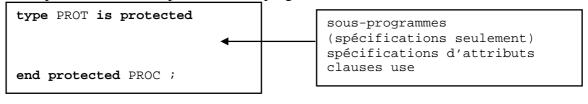

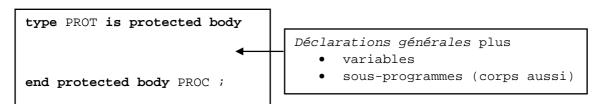

## 2.2.4 Le type protégé (moniteur)

Il s'agit d'une fonctionnalité orientée objet, qui permet de déclarer une zone et des objets dont l'accès est contrôlé de façon qu'un processus au plus ait l'usage de ces objets à un instant donné. Attention : un type protégé est un type, et n'a aucune activité en lui-même ; ce sont les objets déclarés de ce type qui en auront.

En tant que type, il se déclare aux mêmes endroits que les autres types. Il serait baroque toutefois d'en déclarer dans une zone séquentielle (processus, simultané procédural, sousprogramme) puisque les règles de visibilité garantissent déjà la propriété essentielle du type protégé. Les types protégés ont au contraire plutôt vocation à devenir les types de variables partagées. Cette "vocation" devient une obligation à partir des implémentations de VHDL 2000.

Les types protégés se déclarent en deux morceaux, la spécification et le corps. Ces deux morceaux peuvent être dans la même zone déclarative, leur séparation permet les déclarations incomplètes nécessaires pour faire des types récursifs. Bien entendu, le corps doit apparaître après la spécification et compléter les sous-programmes déclarés.

Figure 10 Contenu d'un type protégé

Plus tard, une variable partagée sera déclarée en contexte concurrent : shared variable V : PROT ;

Et les sous-programmes du type protégé seront invoqués par la notation pointées : V.sousprog(arg1,arg2) ;

La propriété de protection est assurée, entre autres, par le fait que les variables locales à cette structure ne peuvent être déclarées que dans le corps du type protégé, et de ce fait sont accessibles seulement par des sous-programmes du même type.

# 2.3 Les sous-programmes

Les sous-programmes sont des zones de code séquentiel, qui n'existent et ne sont actifs que si on les appelle (au contraire des composants instanciés et configurés qui ont une vie pendant toute la simulation, par exemple). Les sous-programmes peuvent être spécifiés dans une déclaration qui ne donne que leur nom et les noms et types des arguments sur lesquels ils

travaillent. Cette spécification peut être isolée, auquel cas il faudra la répéter plus bas en ajoutant le corps du sous-programme. Elle peut se poursuivre par le corps du sous-programme, auquel cas elle ne sera pas répétée. La séparation en deux « morceaux » permet d'une part de confiner l'implémentation aux corps de paquetage en publiant la spécification, d'autre part de permettre l'écriture d'algorithmes à récursivité croisée (A appelle B qui appelle A). Il y a deux catégories de sous-programmes, les procédures et les fonctions.

## 2.3.1 Les arguments

Chaque sous-programme peut avoir une liste d'arguments entre deux parenthèses (pas de parenthèse s'il y a zéro argument) et séparés par des points virgules. Chacun de ces arguments est présenté de la façon suivante :

```

.....[genre] NOM : [mode] TYPE [:= valeur par défaut]...

```

Les zones entre crochet sont optionnelles et ont une valeur par défaut qui peut changer suivant les contextes. Le genre concerne signal/variable/constant/file/quantity/terminal, le mode est in/out/inout/buffer. Tous les genres et tous les modes ne sont pas autorisés partout.

Plusieurs arguments qui partagent exactement la même déclaration peuvent être factorisés et séparés par une virgule : la déclaration sera dupliquée pour chacun d'eux.

```

...Nom1, Nom2 : INTEGER := 3 ;...

```

Si la valeur par défaut est un appel de fonction, cette fonction sera appelée autant de fois qu'il y a d'arguments à initaliser.

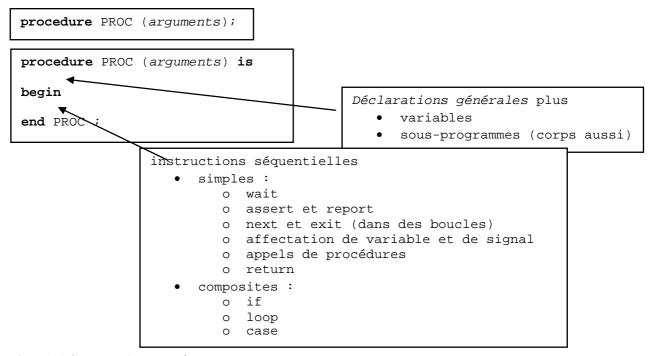

### 2.3.2 La procédure

La procédure est une portion de code séquentiel qu'on invoque en tant qu'instruction : l'appel de procédure est une instruction séquentielle et aussi une instruction concurrente. La spécification donne son nom, et la liste des arguments espérés.

Figure 11 Contenu d'une procédure

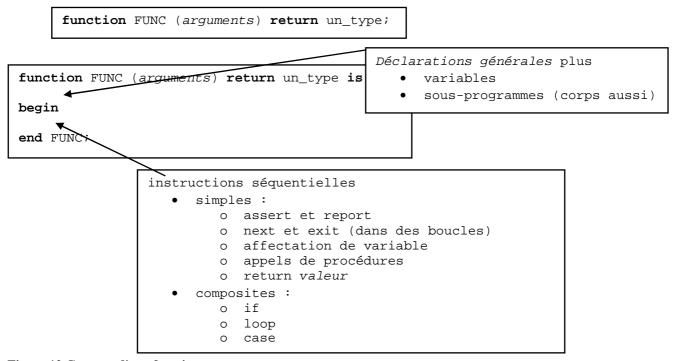

#### 2.3.3 La fonction

La fonction est une portion de code séquentiel qu'on invoque en tant que valeur dans une expression : l'appel de la fonction n'est pas une instruction. La spécification donne son nom, et la liste des arguments espérés avec pour chacun son genre (signal, constante, fichier (file) mais pas variable) son nom, son type, son mode (<u>in forcément</u> qui est par défaut), et sa valeur par défaut éventuelle.

Elle donne aussi le type de la valeur retournée par la fonction.

Figure 12 Contenu d'une fonction

Il y a deux catégories de fonctions : pure et impure.

- Une fonction est pure si elle n'a pas d'effets de bord, c'est-à-dire si ce qu'elle rend ne dépend que de ses arguments, et qu'elle n'écrit rien en dehors de ses variables locales.

- Une fonction est impure si elle a des effets de bord, par exemple une fonction qui compterait combien de fois elle est appelée, ceci nécessitant le maintien d'une variable extérieure à la fonction.

Une fonction se déroule à temps strictement nul (elle fait partie de l'évaluation des expressions). Elle ne peut donc pas contenir d'instruction **wait** ou **break**. Enfin, l'algorithme d'une fonction doit absolument tomber sur un **return**, au contraire de la procédure où cela est optionnel. Cela ferait une erreur à l'exécution si l'exécution passait sur son « **end** ».

2

3

5

6

8

10

11

12

13

14

15

CLÉS DE CE MANUEL

COMPORTEMENTAL

TABLE DES FIGURES

**BIBLIOGRAPHIE**

SYSTÈME

**SWITCH**

**INDEX**

SYNCHRONE **ASYNCHRONE**

ANALOGIQUE

RÉFÉRENCES

HIÉRARCHIE ET STRUCTURE

MODÉLISATION DE BIBLIOTHÈQUES - VITAL

QUOI, OÙ, ZONES DÉCLARATIVES, ZONES D'INSTRUCTIONS

# 3 Environnement, **Bibliothèques**

Les bibliothèques sont, pour le langage, de simples noms logiques : STD, IEEE, etc.; C'est l'installation de l'outil qui redirige ces noms sur les emplacements physiques réels. Quelques unes de ces

- bibliothèques ont un statut spécial: STD est la bibliothèque mère

- indispensable pour faire quoi que ce soit, elle contient le nécessaire paquetage STANDARD. Il est inutile de la mentionner au début d'une unité, par défaut toutes sont préfixées de library STD ; use STD.STANDARD.all ;

- STD.STANDARD c'est là que sont définis les types BOOLEAN, BIT et INTEGER. Or ces types sont utilisés dans le langage lui-même, par exemple BOOLEAN pour les instructions if, BIT pour l'attribut TRANSACTION, INTEGER pour l'élévation à la puissance. C'est pourquoi l'usage de STD est « par défaut », la clause « library STD ; » est implicitement mise au début de chaque unité, avec use STANDARD.all.

- STD.TEXTIO contient des primitives rustiques de lecture et écriture sur fichier et sur console. La base du système d'entrées-sorties est qu'on lit ou on écrit ligne à ligne des chaînes de caractères. La conversion de ces chaînes depuis ou vers des types du langage est à faire par ailleurs, quelques primitives sont fournies dans le paquetage sur les types de STANDARD.

- WORK est la bibliothèque où l'on travaille. C'est le seul endroit où l'on a le droit de compiler. La bibliothèque WORK est vue, par ses clients, sous un autre nom (MARTIN par exemple, depuis chez Dupont). Chaque concepteur a donc « sa » bibliothèque WORK, et accède à celles des autres en donnant leur nom. Il est inutile de la mentionner au début des unités, comme pour STD par défaut toutes les unités sont préfixées de library WORK; (attention, pas de use par défaut).

- IEEE est une bibliothèque qui contient les paquetages standardisés par les IEEE, ainsi que de façon consensuelle des paquetages « presque » standards, mis dans le domaine public par un vendeur par exemple.

- IEEE.STD\_LOGIC\_1164 contient le type à 9 états universellement utilisé par les concepteurs. : 'U' 'X' '0' '1' 'Z' 'W' 'L' 'H' ' -' 'U' pour uninitialized, valeur par défaut déposée au début des simulations et permettant de repérer les signaux qui n'ont pas été initialisés au bout d'un temps raisonnable. Deux systèmes logiques (fort : 01X et faible :LHW –low, high, weak conflict) permettent de gérer les « forces » : en cas de conflit entre un faible et un fort, c'est le fort qui gagne. On peut ainsi modéliser des systèmes « drain ouvert » par exemple. 0/L et 1/H ont le sens logique usuel. X/W signifient « conflit ». Z est la haute impédance, pour un bus que personne ne prend par exemple. Le '-' veut dire « don't care » et ne sert qu'en synthèse (en attendant VHDL 2008, voir §1.7.1.9 page 11) pour permettre de ne pas sur-spécifier et laisser le synthétiseur optimiser (inversement, les valeurs UXW ne servent qu'au simulateur, on ne va pas « spécifier » un conflit).

- IEEE.STD\_LOGIC\_TEXTIO n'est pas standard (il le devient avec VHDL 2008) mais son source est public: c'est un paquetage qui complète utilement TEXTIO en fournissant les primitives de conversion entre chaînes de caractères et les types de STD\_LOGIC\_1164

- o IEEE.STD\_LOGIC\_ARITH contient des primitives fournissant l'arithmétique signée et non signée sur des vecteurs de STD\_LOGIC. C'est un paquetage assez long et le concepteur aura avantage à en inspecter le code pour se rendre compte de ses possibilités. À noter que les opérateurs travaillent sur deux types SIGNED et UNSIGNED, qui ne sont pas compatibles entre eux ni avec STD\_LOGIC\_VECTOR mais qui sont parents, c'est-à-dire qu'on peut toujours changer l'un en l'autre. C'est grâce à ce choix que le même paquetage fournit l'arithmétique entre un entier signé et un entier non signé.

- o IEEE.STD\_LOGIC\_SIGNED et IEEE.STD\_LOGIC\_UNSIGNED sont deux paquetages qui font le choix inverse du précédent : l'arithmétique est fournie directement sur le type STD\_LOGIC\_VECTOR mais du coup on ne peut plus avoir à la fois des nombres signés et non signés, sauf à utiliser la notation pointée ce qui est hostile quand il s'agit d'opérateurs comme « + » ou « ». Par contre plus besoin de changements de types avant d'opérer.

- o IEEE.MATH\_REAL et IEEE.MATH\_COMPLEX deux jeux de primitives mathématiques, qui sont très utilisés en VHDL AMS.

- o [AMS]IEEE.FUNDAMENTAL\_CONSTANTS

- o [AMS]IEEE.MATERIAL\_CONSTANTS

- DISCIPLINES est la bibliothèque utilisée dans le monde analogique et qui contient les déclarations pertinentes de natures et de constantes pour les différents domaines physiques que l'on veut modéliser.

- o DISCIPLINES.ENERGY\_SYSTEMS

- o DISCIPLINES.ELECTRICAL\_SYSTEMS

- o DISCIPLINES.MECHANICAL SYSTEMS

- o DISCIPLINES.THERMAL\_SYSTEMS

- o DISCIPLINES.FLUIDIC SYSTEMS

- o DISCIPLINES.RADIANT\_SYSTEMS

Les implémentations confondent parfois DISCIPLINES avec IEEE. C'est une des corrections que l'on peut être amené à faire quand on porte un modèle.

### 4 Hiérarchie et Structure

```

CLÉS DE CE MANUEL

QUOI, OÙ, ZONES DÉCLARATIVES, ZONES D'INSTRUCTIONS

2

3

ENVIRONNEMENT, BIBLIOTHÈQUES

4

5

MODÉLISATION DE BIBLIOTHÈQUES - VITAL

SYSTÈME

7

COMPORTEMENTAL.

8

SYNCHRONE

ASYNCHRONE

10

SWITCH

11

ANALOGIQUE

12

RÉFÉRENCES

13

INDEX

14

TABLE DES FIGURES

15

BIBLIOGRAPHIE

```

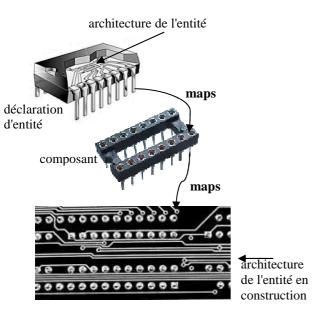

Il y a deux niveaux de branchement dans une architecture: D'une part le composant, sorte de support, est connecté aux signaux et aux ports de l'architecture dans laquelle il est instancié. D'autre part l'entité est connectée à son composant, soit par une spécification de configuration – cela se passe dans l'architecture elle-même - soit par une déclaration de configuration –ce qui se fait depuis l'extérieur, dans une unité de conception spécifique, la déclaration de configuration-. À chaque étage, on peut spécifier les génériques, et les branchements.

Figure 13 L'instance du composant et sa configuration avec une entité demandent deux « port map » et deux « generic map »

# 4.1 La généricité

Les entités et les composants peuvent être génériques ; la généricité consiste à déclarer une constante dans une zone spéciale, après le mot-clé **generic**, et à ne donner sa valeur que plus tard. Cela peut être au moment d'instancier un composant, au moment de le configurer ou carrément au moment de simuler ou de synthétiser.

Il y a plusieurs cas de figure.

## 4.1.1 L'entité est générique, le composant est pareillement générique

```

entity SHIFTN is

generic (N : INTEGER ; delay: TIME);

port (inp: BIT_VECTOR(N-1 downto 0); outp: out BIT_VECTOR(N-1 downto 0))

end entity ADDN;

component COMP is

generic (X : INTEGER ; delay: TIME);

port (E: BIT_VECTOR(N-1 downto 0); S: out BIT_VECTOR(N-1 downto 0))

end component ADDN;

```

On configure le composant avec cette entité là:

On ne donne pas de valeur, on attache un argument à l'autre. Noter ici que si les arguments de l'entité et du composant avaient le même nom et le même ordre, on pourrait compter sur les liens par défaut et ne pas écrire les branches **generic map** et **port map**. On verra par ailleurs qu'on n'est pas obligé de d'attacher les ports tels quels (voir §4.2 page 29).

L'instance de composant fixe enfin la généricité du composant générique:

```

CX: COMP generic map (X=>8, delay=> 2 ns) port map (E=>P1, S=>P2);

```

Ces valeurs (8 et 2 ns), fournies à la généricité du composant, sont transmises à celle de l'entité qui s'en sert comme d'une constante dans ses architectures.

Dans ce cas de figure, le composant et sa configuration restent « virtuels » jusqu'au moment où l'on instancie le composant en fournissant les valeurs qui manquent. On peut donc, immédiatement dessous, instancier un autre composant de la même entité avec d'autres arguments génériques :

```

CY: COMP generic map (X=>16, delay=> 4 ns) port map (E=>P3,S=>P4);

-- CY est sur 16 bits et 4 ns.

```

### 4.1.2 L'entité est générique, pas le composant

```

entity SHIFTN is

generic (N : INTEGER ; delay: TIME);

port (inp: BIT_VECTOR(N-1 downto 0); outp: out BIT_VECTOR(N-1 downto 0))

end entity ADDN;

component COMP is

port (E: BIT_VECTOR(7 downto 0); S: out BIT_VECTOR(7 downto 0))

end component ADDN;

```

On configure le composant avec cette entité là, mais il nous faut dire combien valent *N* et *delay* pour que ça marche:

L'instance de composant voit un composant qui n'est pas générique:

```

CX: COMP port map (E=>P1, S=>P2);

```

Si l'on instancie un autre composant de ce type, ce sera forcément le même (8, 3 ns) contrairement à ce que l'on a fait au paragraphe précédent.

```

CY: COMP port map (E=>P3, S=>P4); -- CY est aussi sur 8 bits et 3 ns.

```

Ceci n'est pas le signe d'une infériorité de cette méthode. D'une part on n'a pas souvent le choix, les bibliothèques étant importées ou achetées telles quelles ; d'autre part si l'on ne veut se servir que de tel composant en multiples exemplaires identiques, il est inutile et pénible, voire peu optimisable pour le simulateur, de repousser au dernier moment la donnée de ses paramètres.

### 4.1.3 L'entité est générique, le composant aussi mais moins

Voyons le cas où l'entité a deux arguments génériques, et le composant un seul.

```

entity SHIFTN is

generic (N : INTEGER ; delay: TIME);

port (inp: BIT_VECTOR(N-1 downto 0); outp: out BIT_VECTOR(N-1 downto 0))

end entity ADDN;

component COMP is

generic (delay: TIME);

port (E: BIT_VECTOR(7 downto 0); S: out BIT_VECTOR(7 downto 0))

end component ADDN;

```

On configure le composant avec cette entité là, mais il nous faut dire combien vaut *N* et passer *delay* comme argument générique restant:

L'instance de composant voit un composant qui n'est générique que sur *delay*:

```

CX: COMP generic map (delay=> 2 ns) port map (E=>P1,S=>P2);

```

D'autres instances du même composant pourront faire varier delay, mais pas N:

```

CY: COMP generic map (delay=> 4 ns) port map (E=>P3, S=>P4);

-- CY est sur 8 bits avec un délai de 4 ns.

```

On utilisera cette fixation partielle de la généricité lors de la configuration chaque fois que l'on voudra utiliser une entité très générique venant d'une bibliothèque achetée ou non maîtrisée, sur un composant dont la généricité « nous suffit ».

# 4.2 Les ports

De même qu'il y a double *mapping* pour la généricité, de même pour les ports. Les ports représentent la connexion des composants à l'architecture, et de l'entité au composant. VHDL fournit dans le langage tous les « bidouillages » que peut s'autoriser un concepteur de cartes imprimées :

- changer l'ordre des pattes,

- en laisser certaines « en l'air » en sachant qu'elles sont tirées à une valeur donnée

- en forcer d'autres à la masse ou à une valeur donnée,

- en changer le type (passer de la logique 5V à 3V)

- n'utiliser que la moitié d'un bus ou en reconstruire un avec deux moitiés

- et, qui plus est, aux deux niveaux de l'instance et de la configuration.

Attention: l'utilisation d'une de ces facilités n'est pas exclusive des autres. En poussant VHDL et ses facilités d'associations dans ses derniers retranchements, on peut arriver à des modèles complètement illisibles et qui sont de vraies gageures à exécuter pour les outils de CAO. À utiliser avec autant de modération que les breuvages à radicaux COOH, sinon le mal de tête subséquent est de même nature.

### 4.2.1 L'ordre des ports

Supposons que l'entité correspond parfaitement au composant, mais hélas l'ordre ou la numérotation des ports n'est pas le même.

```

entity E is

port (A, B, C : BIT ; S : out BIT) ;

end entity E;

component C is

port (T: out BIT; X, Y, Z: BIT)

end component;

```

Nous allons utiliser l'association par nom, qui permet de s'affranchir des questions de position:

```

for CX: C use entity LIB.E port map (A=>X, B=>Z, C=> Y, S => T);

```

La même syntaxe d'association fonctionne pour l'instance :

```

CX : C port map (X=> P1, Y=> P2, Z=> P3, S=> P4) ;

```